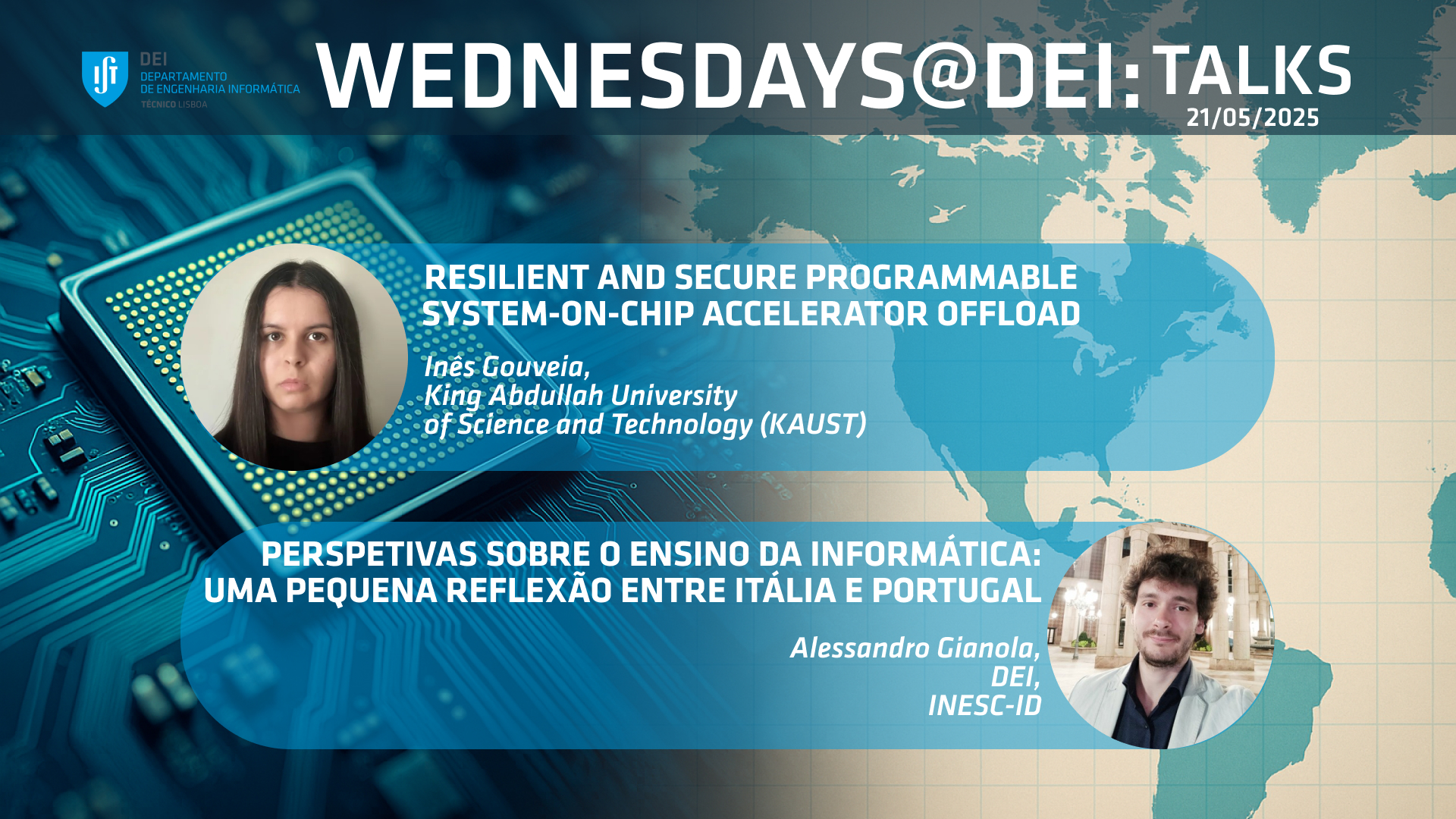

Wednesdays@DEI: Talks, 21-05-2025

Author and Affiliation: Inês Gouveia, King Abdullah University of Science and Technology (KAUST)

Bio: Dr. Inês Gouveia is a Postdoctoral Research Fellow at the King Abdullah University of Science and Technology (KAUST), working on security and resilience of system-on-chip (SoC) architectures for FPGA acceleration, dynamic bitstream reconfiguration for secure application flexibility, hardware acceleration of intrusion detection neural networks, specification-based automation of hardware fuzzing log analysis, and network-on-chip recovery.

Before coming to KAUST, she worked as a Research Scientist at Intel Labs, where she explored safety features in the realms of open-source hardware and chiplets. In 2022, she obtained her Ph.D. from the University of Luxembourg where she researched architectural support for hypervisor-level intrusion tolerance in SoCs. In the same year, she briefly worked as a Research Associate in the same university, looking into NoC security and HLS-based matrix multiplication accelerators.

Her Bachelor's and Master's studies were completed at the University of Lisbon, where she also worked as a Junior Researcher working on non-intrusive runtime verification

Title: Resilient and secure programmable system-on-chip accelerator offload

Abstract: The trend of offloading computing to hardware accelerators is gaining more traction in emerging systems and applications seeking accelerated computing and enhanced security. To continuously support new use-cases while reducing the burden of hardware fabrication of a monolithic system (costly and slow), these systems are often assembled and deployed as system-on-chip (SoCs) that makes use of modular, cheap commercial-of-the-shelf components. Plus, they leverage the hardware programmablity features of general-purpose reconfigurable hardware like FPGAs for performance and cost (namely power) reduction. Unfortunately, this raises new computing integrity challenges against intrusions and faults.

In this talk I will discuss these challenges and introduce Samsara, a resilient and secure computing platform architecture for programmable SoCs, hinging on hardware reconfigurability to ensure computing integrity by employing state-machine replication and hardware rejuvenation of accelerator tiles.

--

Author and Affiliation: Alessandro Gianola, DEI, INESC-ID

Title: Perspectives on teaching computer science: a short reflection between Italy and Portugal

Abstract: In this presentation, I will share my personal, direct, and indirect experience acquired in four higher education institutions in Italy and Portugal: the Università degli Studi di Milano (Mathematics), the Libera Università di Bolzano (Computer Science), the Politecnico di Milano (Computer Engineering) and Instituto Superior Técnico (Computer Science and Engineering). It is a path that is not entirely homogeneous, intersecting different areas — from mathematics to computer science — and distinct institutional contexts.

The session will be informal, aiming to serve as a starting point for exchanging ideas and promoting open and enriching discussions. Topics to be addressed include the structure and content of course units, the organization of theoretical and practical classes, evaluation methods and exams, logistical aspects, as well as the cultural dimensions that shape the relationship between students and faculty.

The objective is to encourage a collective reflection on the future of computer science education at Técnico, drawing from the contrasts and similarities with some experiences in the educational landscape of northern Italy.