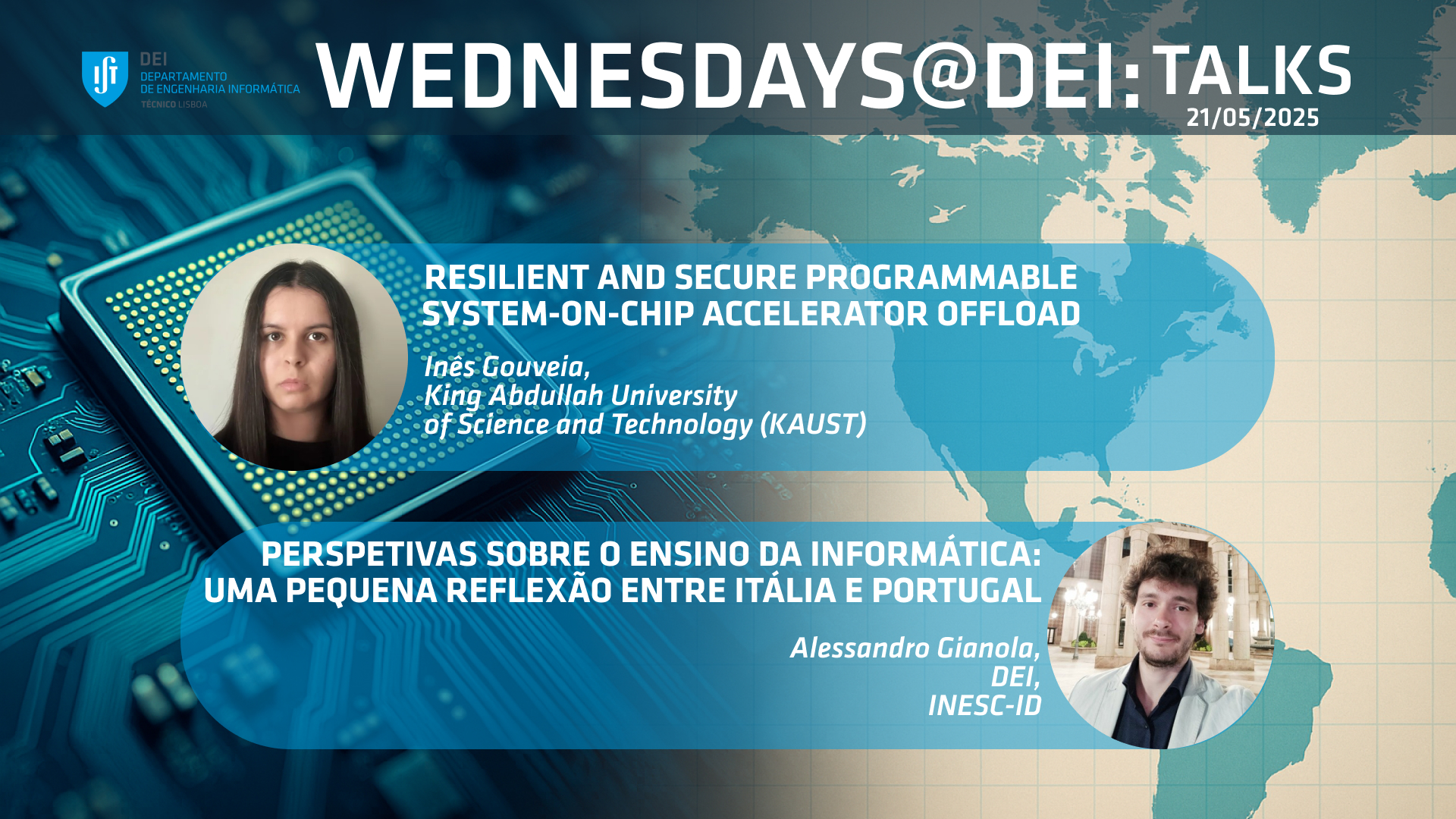

Wednesdays@DEI: Talks, 21-05-2025

Autor e vínculos: Inês Gouveia, King Abdullah University of Science and Technology (KAUST)

Bio: Dr. Inês Gouveia is a Postdoctoral Research Fellow at the King Abdullah University of Science and Technology (KAUST), working on security and resilience of system-on-chip (SoC) architectures for FPGA acceleration, dynamic bitstream reconfiguration for secure application flexibility, hardware acceleration of intrusion detection neural networks, specification-based automation of hardware fuzzing log analysis, and network-on-chip recovery.

Before coming to KAUST, she worked as a Research Scientist at Intel Labs, where she explored safety features in the realms of open-source hardware and chiplets. In 2022, she obtained her Ph.D. from the University of Luxembourg where she researched architectural support for hypervisor-level intrusion tolerance in SoCs. In the same year, she briefly worked as a Research Associate in the same university, looking into NoC security and HLS-based matrix multiplication accelerators.

Her Bachelor's and Master's studies were completed at the University of Lisbon, where she also worked as a Junior Researcher working on non-intrusive runtime verification

Título: Resilient and secure programmable system-on-chip accelerator offload

Resumo: The trend of offloading computing to hardware accelerators is gaining more traction in emerging systems and applications seeking accelerated computing and enhanced security. To continuously support new use-cases while reducing the burden of hardware fabrication of a monolithic system (costly and slow), these systems are often assembled and deployed as system-on-chip (SoCs) that makes use of modular, cheap commercial-of-the-shelf components. Plus, they leverage the hardware programmablity features of general-purpose reconfigurable hardware like FPGAs for performance and cost (namely power) reduction. Unfortunately, this raises new computing integrity challenges against intrusions and faults.

In this talk I will discuss these challenges and introduce Samsara, a resilient and secure computing platform architecture for programmable SoCs, hinging on hardware reconfigurability to ensure computing integrity by employing state-machine replication and hardware rejuvenation of accelerator tiles.

--

Autor e vínculos: Alessandro Gianola, DEI, INESC-ID

Título: Perspetivas sobre o ensino da informática: uma pequena reflexão entre Itália e Portugal

Resumo: Nesta apresentação, vou partilhar a minha experiência pessoal, direta e indireta, adquirida em quatro instituições de ensino superior, entre Itália e Portugal: a Università degli Studi di Milano (Matemática), a Libera Università di Bolzano (Informática), o Politecnico di Milano (Engenharia Informática) e o Instituto Superior Técnico (Engenharia Informática). Trata-se de um percurso não totalmente homogéneo, que cruza diferentes áreas — da matemática à informática — e contextos institucionais distintos.

De carácter informal, a sessão pretende ser um ponto de partida para a troca de ideias e a promoção de discussões abertas e enriquecedoras. Serão abordadas questões como a estrutura e o conteúdo das unidades curriculares, a organização das aulas teóricas e práticas, os métodos de avaliação e os exames, os aspetos logísticos, bem como as dimensões culturais que moldam a relação entre estudantes e docentes. O objetivo é estimular uma reflexão coletiva sobre o futuro do ensino da informática no Técnico, a partir do contraste e das semelhanças com algumas experiências no panorama do norte da Itália